# PRISM™ 2.4GHz Chip Set

**Direct Sequence Spread Spectrum Wireless Transceiver Chip Set**

October 1996

#### **Features**

- Provides Antenna-to-Bits™ Data Stream

- Low Voltage Operation from 2.7V to 5.5V

- 2.4GHz 2.5GHz ISM Band Operation

- Single Heterodyne Conversion

- Programmable Antialiasing and Shaping Filters

- 10MHz to 400MHz IF Operation with RSSI

- Autonomous Half Duplex Direct Sequence Modem

- Selectable DBPSK, DQPSK Signalling

- · Antenna Diversity Selection

- Direct Sequence Physical Layer (DS-PHY)

- · Differential Data Encoding/Decoding

- Programmable 16-Bit PN Code

- Data Rates up to 4 MBPS DQPSK

- Power Management Control

- Low Profile PCMCIA-Compatible Surface Mount **Packaging**

### **Applications**

- Systems Targeting IEEE 802.11 Standard

- PCMCIA Wireless Transceiver

- **WLAN RF Modems**

- TDMA Packet Protocol Radios

- Part 15 Compliant Radio Links

### ™ Description

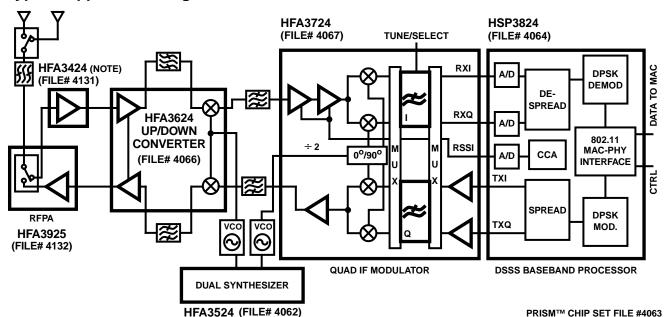

The Harris 2.4GHz PRISM™ chip set is a highly integrated five-chip solution for RF modems employing Direct Sequence Spread Spectrum

(DSSS) signaling. Significant integration of transmit and receive functions employ the following ICs: complete integrated DSSS engine, the HSP3824; a quadrature modulator/demodulator, integrated with an IF limiter amplifier with RSSI, the HFA3724; a combined LNA/Mixer and upconverter/preamplifier, the HFA3624; a high performance, low noise amplifier for increased receiver sensitivity, the HFA3424; a dual synthesizer, the HFA3524 and a monolithic RF power amplifier, the HFA3925. Each of the functions may be used individually or in any combination in support of a variety of RF modem applications.

The PRISM™ chip set is intended to support various data rates including systems targeting the proposed IEEE 802.11 standard "Direct Sequence Physical layer (DS-PHY)". Differential BPSK and QPSK signaling is employed with differential encoding and decoding of packetized data. A PN sequence rate of up to 22 MCPS is supported for up to a 16 chip PN code. Integrated programmable low pass filters are used on the HFA3724 to allow chip rates from 2.75 MCPS to 22 MCPS. A flexible general purpose data and control interface is provided for parameter configuration and for transferring data packets between the PHY and Media Access Control (MAC) layers. Data rates of up to 2 MBPS for DBPSK and 4 MBPS for DQPSK are supported.

## Typical Application Diagram

NOTE: Required for systems targeting 802.11 specifications.

PRISM™, the PRISM™ logo and Antenna-to-Bits™ are trademarks of Harris Corporation.

#### Typical 802.11 DS-PHY System Level Performance (Note 5) (Measured at a diversity antenna port)

| Receiver                                      | Transmitter                                      |

|-----------------------------------------------|--------------------------------------------------|

| • Frequency Range 2.4GHz - 2.4835GHz          | • Frequency Range                                |

| • Step Size                                   | • Step Size1MHz                                  |

| Cascaded Noise Figure 6.8dB                   | Output Power                                     |

| • Sensitivity93dBm, 1 MBPS, 8E-2 FER (Note 1) | • Spurious Outputs Targeting ISM/802.11          |

| -90dBm, 2 MBPS, 8E-2 FER (Note 1)             | • Transmit Spectral Mask32dBr at First Side-Lobe |

| • Input Intercept Point17dBm                  | • IF Frequency                                   |

| • IF Frequency                                | • Supply Voltage 2.7V - 5.5V                     |

| • IF Bandwidth                                | General Specifications                           |

| • Image Rejection                             | Targeted Standard IEEE 802.11                    |

| <ul><li>Adjacent Channel Rejection</li></ul>  | Data Rate                                        |

|                                               | • Range                                          |

|                                               | • RX/TX Switching Speed 2μs                      |

|                                               | Standby Current                                  |

|                                               | - Mode 1: 240mA at 1μs Recovery (Notes 3, 4)     |

#### NOTES:

- 1. FER = Frame Error Rate or Packet Error Rate.

- 2. Range Test using AND-C-107 omnidirectional antenna.

- 3. Supply current includes AM79C930 MAC Processor.

- 4. Recovery time is for the PRISM™ 2.4GHz Chip Set only and does not include programming latency of the AM79C930 MAC Processor.

- 5. Refer to Application Note AN9624 for more information on the "PRISM™ DSSS PC Card Wireless LAN Description".

All Harris Semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Harris Semiconductor products are sold by description only. Harris Semiconductor reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Harris is believed to be accurate and reliable. However, no responsibility is assumed by Harris or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Harris or its subsidiaries.

### Sales Office Headquarters

For general information regarding Harris Semiconductor and its products, call 1-800-4-HARRIS

#### **NORTH AMERICA**

Harris Semiconductor P. O. Box 883, Mail Stop 53-210 Melbourne, FL 32902 TEL: 1-800-442-7747

(407) 729-4984 FAX: (407) 729-5321

#### **EUROPE**

Harris Semiconductor Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

#### ASIA

> Harris Semiconductor PTE Ltd. No. 1 Tannery Road Cencon 1, #09-01 Singapore 1334 TEL: (65) 748-4200 FAX: (65) 748-0400